FPGA简介

FPGA是什么

FPGA 就是一个可以通过编程来改变内部结构的芯片

FPGA基本结构

触发器(FF)和查找表( LUT)

Vivado使用

软件安装

根据CPU设计实战:LoongArch版-Vivado的安装学习Vivado的安装

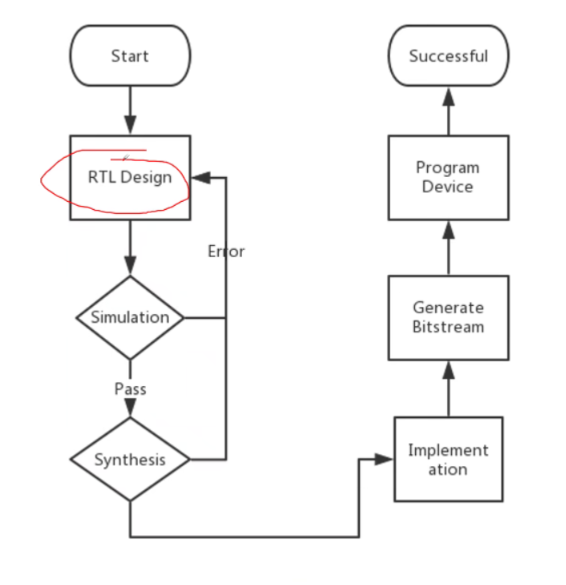

设计流程

RTL设计-仿真-综合-实现-生成比特流

细节可以参考CPU设计实战:LoongArch版- FPGA 的设计流程

软件使用

根据CPU设计实战:LoongArch版学习Vivado的基本用法

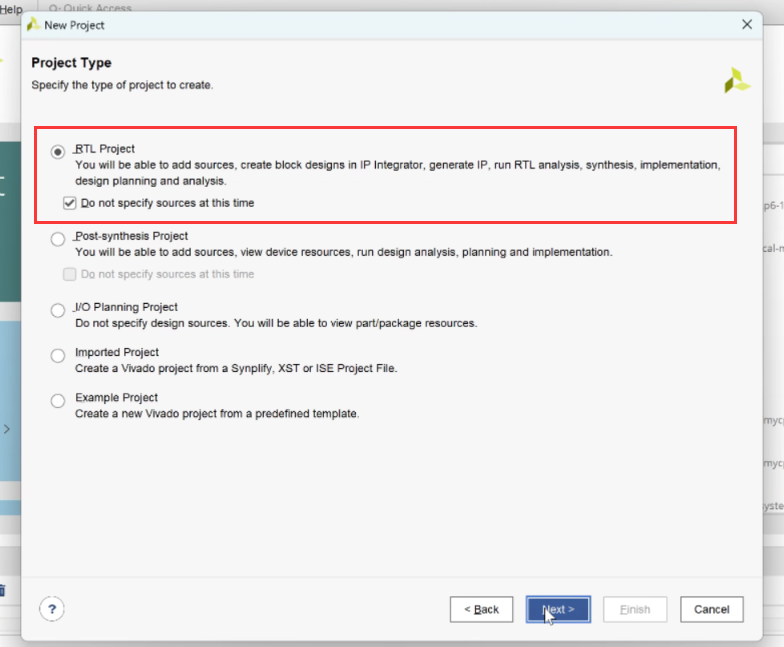

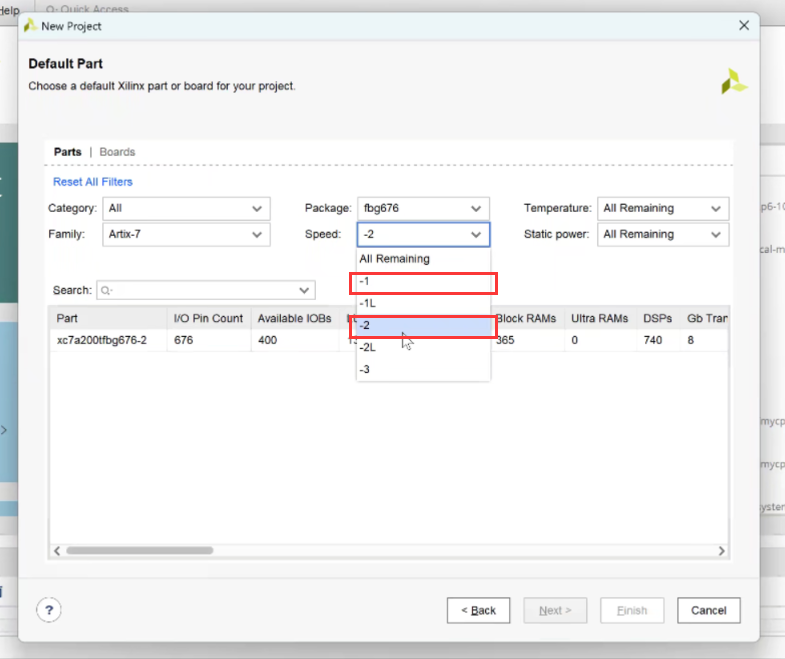

使用Vivado要注意的两个选择:

-

选择RTL级

-

理论上速度-1、-2均可选择;比赛要求团体选择-1,个人选择-2

Verilog使用

数据类型

Verilog 最常用的 2 种数据类型就是线网 wire 与寄存器 reg ,其余类型可以理解为这两种数据类型的扩展或辅助。

变量定义示例

reg rega; //定义了一个1位的名为rega的reg型数据

reg[3,0] regb,regc; //定义了一个4位的名为regb和regc的reg型数据

变量赋值方法示例

assign a = b & c; //采用assign是描述组合逻辑最常用方法

//“<=”非阻塞赋值

//常用于always块语句

{b,{3{a,b}}}//位拼接运算符,等同于{b,a,b,a,b,a,b}

always语句和module模块

always语句

//电平触发的always块常常用来描述组合逻辑的行为

//上沿

always @(posedge clock)

begin

...

end

//沿触发的always块常常描述时序行为

//@(*)和@*都表示对其后面语句块中所有输入变量的变化是敏感的

always @(*)

begin

...

end

//多个always块并没有前后之分

在”always”块内,如果在给定的条件下变量没有赋值,这个变量将保持原值,也就是说会生成一个锁存器:

- 如果用到

if语句,最好写上else项。 - 如果用

case语句,最好写上default项。

遵循以上可以避免发生综合之后生成锁存器的现象。

😥没搞清楚怎么换掉highlight.min.js,对Verilog语言的支持还要等一段时间

把head和footer改了下,先用着

ok,解决了!